免费下载

免费下载

大小:655.2MB

下载:次

modelsim(HDL语言仿真软件)

del 模拟 调节 HD in on strong System 2 X

- 支 持:Windows操作系统

- 分 类:软件下载

- 大 小:655.2MB

- 开发者:梦幻小优

- 提 现:952

- 说 明:v10.5a 中文版

- 下载量:次

- 发 布:2024-09-06 09:24:17

手机扫码免费下载

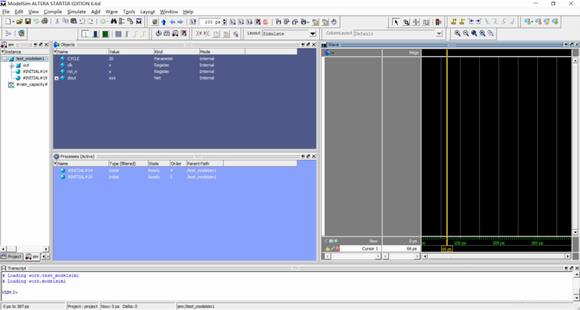

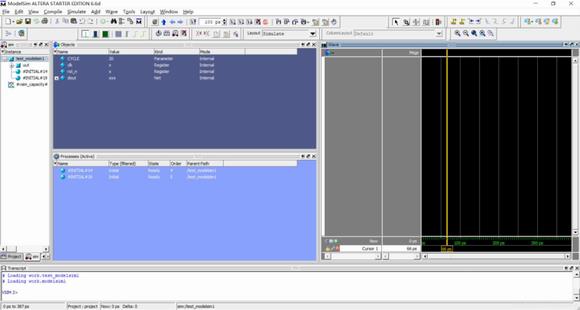

纠错留言#modelsim(HDL语言仿真软件)截图

#modelsim(HDL语言仿真软件)简介

modelsim破解版下载是业内十分出色的HDL语言表达烧录器,全方位适用UNIX(包含64位)、Linux和Windows平台,是作FPGA/ASIC设计方案的RTL级和门级电路设计的优选,选用立即提升的编译程序技术性、Tcl/Tk技术性、和单一核心模拟仿真,编译程序模拟仿真速度更快,编译程序的编码与服务平台不相干,给予最友善的调节自然环境,可以为客户给予全方位健全及其性能卓越的认证作用,此外也有人性化的用户界面和客户插口,为客户加速调错给予强大的方式,是FPGA/ASIC设计方案的优选模拟仿真软件,有这方面需要的客户可以在这儿下载并安装。

modelsim汉化版APP详细介绍:

ModelSim有几种不一样的版本号:SE、PE、LE和OEM,在其中SE是最高级别的版本号,而集成化在 Actel、Atmel、Altera、Xilinx及其Lattice等FPGA生产商设计工具中的均是其OEM版本。

SE版和OEM版在功能性和功能层面有很大区别,例如针对大家都关注的模拟仿真速率问题,以Xilinx企业开具的OEM版本ModelSim XE为例子,针对编码低于40000行的设计方案,ModelSim SE 比ModelSim XE要快10倍;针对编码超出40000行的设计方案,ModelSim SE要比ModelSim XE快近40倍。

有se、de、pe等好几个版本号,相匹配Altera和Xilinx也有相匹配的OEM版本,全部的版本号作用最強速率较快的便是se,总之也是要破译,当然就装最強的版本号了,和Altera网站上的modelsim的区分取决于,se的版本号大家必须自身编译程序相匹配的库,因此Altera和Xilinx的全是内置相匹配的库不用编译程序的,像我这样与此同时装了Quartus II和ISE的,当然或是自身编译程序便捷一点。

modelsim汉化版APP优点:

统一的混和语言表达仿真模拟模块,便于运用和特性

适用 Verilog,SystemVerilog开展设计方案,VHDL和SystemC,以合理地认证繁杂的设计方案自然环境

迅速调节,便于应用,多语言表达调节自然环境

高級编码遮盖和分析工具,可迅速遮盖封闭式

我nteractive和Post-SIM卡调节用以2个可以用,因而同样的调节自然环境

强劲的波型较为便捷剖析差别和不正确

统一遮盖数据库查询,具备完善的互动式和HTML汇报和解决作用,可以在所有新项目中掌握和调节覆盖面积

再加上HDL Designer和HDL做为详细的设计方案写作,项目风险管理和交互作用的创作者

语句覆盖:运作期内实行的句子数

支系遮盖:危害HDL实行控制流的关系式和case语句

标准遮盖:将支系上的标准转化成使結果为真或假的原素

表述遮盖:与标准遮盖同样,但包含并行处理数据信号分派而不是支系决策

关键表述遮盖:以明确遮盖結果中关系式的各个单独键入的形式展现表述遮盖数据信息

提高的转换遮盖:在默认设置方式下,记数从低于高和从高到低的变换; 在拓展方式下,记数到X的变换

有状态机遮盖:我国和我国衔接遮盖

modelsim汉化版APP特点:

· RTL和门级提升,当地编译程序构造,编译程序模拟仿真速度更快,混合开发跨版本号模拟仿真;

· 单核心VHDL和Verilog混和模拟仿真;

· 源码模板和小助手,项目风险管理;

· 集成化了特性剖析、波型较为、编码遮盖、数据流分析ChaseX、Signal Spy、虚似目标Virtual Object、Memory对话框、Assertion对话框、源代码对话框表明数据信号值、数据信号标准中断点等诸多调节作用;

· C和Tcl/Tk插口,C调节;

· 对SystemC的立即适用,和HDL随意混和;

· 适用SystemVerilog的设计方案作用;

· 系统对级描述语言的最全方位适用,SystemVerilog,SystemC,PSL;

· ASIC Sign off。

· 可以直接或与此同时开展个人行为(behavioral)、RTL级、和门级(gate-level)的编码。

modelsim汉化版APP闪光点:

1、高級代码覆盖率

ModelSim的高級编码遮盖作用和便捷性减少了运用这一珍贵认证資源的阻碍。

ModelSim高級编码遮盖作用为系统验证给予了有價值的指标值。 全部遮盖信息内容都储存在统一遮盖数据库查询(UCDB)中,该数据库查询用以采集和管理方法高效率数据库查询中的全部遮盖信息内容。 可以应用剖析代码覆盖率数据信息的普及率应用工具,比如合拼和检测排行。 遮盖結果可以互动式查询,仿真模拟后或多次仿真模拟运作合拼后查询。 编码遮盖衡量可以按案例或制作企业汇报,进而给予管理方法遮盖数据信息的灵敏性。

适用的遮盖种类包含:

申明报导

运作期内实行的句子数

支行报导

危害HDL实行控制流的关系式和case语句

标准遮盖

将支系上的标准溶解为使結果为true或false的原素

表述范畴

与标准遮盖同样,但包含高并发数据信号分派而不是支系管理决策

重点关注表述

以明确遮盖結果的关系式的各个单独键入的形式展现表述普及率数据信息

提高的转换覆盖面积

在默认设置方式下,记数从低于高和从高到低的变换;在拓展方式下,测算与X的变换

有限状态机遮盖

州宦游的衔接覆盖面积

2、混和HDL模拟仿真

ModelSim将模拟仿真特性和容积与仿真模拟好几个控制模块和系统软件及其完成ASIC门等级签核需要的编码遮盖和调节作用紧密结合。 全方位适用Verilog,SystemVerilog for Design,VHDL和SystemC为单语言表达和多语言表达设计方案认证自然环境给予了稳固的基本。 ModelSim便于应用且统一的调节和模拟仿真自然环境为现如今的FPGA设计方案工作人员给予了她们持续上升的高端作用及其使它们的工作中有效率的自然环境。

3、合理的调节自然环境

ModelSim调节自然环境为Verilog,VHDL和SystemC给予了普遍的形象化作用,使其变成ASIC和FPGA设计方案的优选。

ModelSim根据智能化设计的调节自然环境简单化了发觉设计方案问题的全过程。 ModelSim调节自然环境合理地表明设计方案数据信息,便于剖析和调节全部语言表达。

ModelSim容许在储存結果的模拟仿真后及其即时模拟仿真运作期内应用很多调节和剖析作用。比如,coverage查看器应用代码覆盖率結果剖析和注解源码,包含FSM情况和变换,句子,关系式,支系和转换普及率。

数据信号值可以在源对话框中注解并在波型查看器中查询,进而简单化了目标以及申明中间及其浏览文档中间的超链导航栏的调节导航栏。

可以在目录和波型对话框中剖析市场竞争标准,增加量和事件主题活动。可以轻轻松松界定客户界定的枚举值,便于迅速地掌握仿真模拟結果。为了更好地提升调节高效率,ModelSim还具备图型和文字数据流分析作用。

ModelSim与Mentor的旗舰级手机模拟器Questa®分享一个相同的系统化和操作界面。这使顾客可以轻松升级到Questa,由于她们必须更好的功能并适用高級认证作用。

Modelsim主要特点RTL和门级提升,当地编译程序构造,编译程序模拟仿真速度更快,混合开发跨版本号模拟仿真;

单核心VHDL和Verilog混和模拟仿真;

源码模板和小助手,项目风险管理;

集成化了特性剖析、波型较为、编码遮盖、数据流分析ChaseX、Signal Spy、虚似目标Virtual Object、Memory对话框、Assertion对话框、源代码对话框表明数据信号值、数据信号标准中断点等诸多调节作用;

C和Tcl/Tk插口,C调节;

对SystemC的立即适用,和HDL随意混和;

适用SystemVerilog的设计方案作用;

系统对级描述语言的最全方位适用,SystemVerilog,SystemC,PSL;

ASIC Sign off。

可以直接或与此同时开展个人行为(behavioral)、RTL级、和门级(gate-level)的编码。

modelsim汉化版APP內容:

1、更智能化的GUI

智能化设计的GUI可以合理运用桌面上室内空间。 ModelSim给予了相对高度形象化的互动式图型原素(对话框,菜单栏,菜单栏等)排序方法,使您可以轻轻松松查询和浏览其很多强劲作用。 結果就是便于应用且可以迅速把握的功能丰富的GUI。 根据将Tcl操作界面集成化到其HDL烧录器中,ModelSim彻底改变了模拟仿真的开放式。 Tcl是一种简易但功能齐全的开发语言,用以调节和拓展应用软件。

ModelSim GUI给予高效率的设计方案调节和剖析作用及其新项目和文档管理。

2、记忆力窗

储存器对话框容许形象化,灵便地查询和调节设计方案储存器。 VHDL和Verilog运行内存是以源中全自动获取并在GUI中查询的,进而给予了强有力的检索,添充,编缉,载入和储存作用。运行内存对话框适用文本文件或根据应用匀速运动,任意和测算值来预加载运行内存,进而节约了仅载入运行内存来复位测试平台一部分的用时流程。全部作用都能够根据命令应用,进而可以在脚本制作中应用他们。

3、波型和結果查询

ModelSim给予了性能卓越的多功能波型对话框。 Wave对话框给予了用以标识有意思的时间点并精确测量鼠标光标中间的時间间距的鼠标光标。波型对话框的主要内容可以根据强有力的虚似数据信号界定和分类灵便地设定文件格式。

在2个模拟仿真結果中间可以随意开展波型较为。根据客户特定的時间过虑作用,可以简单解决RTL和门级模拟仿真結果中间的时钟频率差别。

ModelSim给予了与众不同的WLF管理方法应用工具(别名WLFMAN),该应用工具容许解决WLF結果文档。这使您可以特定要纪录到WLF文档的数据量,并容许您依据数据信号或時间对目前WLF文档开展非空子集化。

WLFMAN应用工具可合理管理方法储存空间并提升仿真模拟后调节高效率。

4、源对话框模版和指导

应用VHDL和Verilog模版和指导,您可以快速开发HDL编码,而无须记牢准确的语言表达英语的语法。只需点击电脑鼠标,就可以应用全部语言表达构造。便于应用的指导将正确引导您逐渐进行更繁杂的HDL块的建立。指导表明了怎样建立可参数化设计的逻辑性块,测试台鼓励和设计方案目标。源码对话框模版和指导根据省时的快捷方式图标使初学者和高級HDL开发者获益。

5、项目主管

新项目管理工具大大减少了机构文档和库所需的時间。在编译程序和仿真模拟时,新项目管理工具会储存每一个新项目的唯一设定,使您可以从之前终断的地区重启手机模拟器。模拟仿真特性使您可以更好地应用事先配备的主要参数开展模拟仿真。

6、代码覆盖率

设计方案认证的安全性可以根据代码覆盖率来考量。 ModelSim适用句子,关系式,标准,转换和FSM覆盖面积。代码覆盖率指标值是以HDL源全自动得到的。由于建立了很多可配备和可循环使用的设计方案控制模块,而且并不是全部指标值都很有使用价值,因而可以应用代码覆盖率电脑浏览器中规定的源码应用工具和清除项来灵便管理方法代码覆盖率指标值。

7、根据结论的认证

ModelSim给予了一个全方位的,根据规范的根据结论的认证(ABV)解决方法,可以挑选SystemVerilog结论(SVA),特性标准语言表达(PSL)或二者。

8、强劲的,具备成本效益的仿真模拟

解决方法ModelSim给予了功能齐全的模拟仿真解决方法,特别适合认证大中小型FPGA设计方案;尤其是具备繁杂每日任务重要作用的设计方案。

modelsim汉化版破解教程:

1、在本网站在线下载并缓解压力,获得modelsim-win64-10.5-se.exe程序安装和crak破译文件夹名称,双击鼠标主程序执行安裝,点一下下一步

2、点一下访问挑选安装路径,点一下下一步

3、点一下允许

4、正在安装中,時间会非常长,耐心等待一会儿

5、建立桌面快捷方式,点一下是

6、必须重新启动电子计算机,点一下是

7、选定Modelsim SE 10.5,鼠标右键,双击鼠标开启程序安装部位,将crak破译文件夹名称中的MentorKG.exe、mgls.dll及其patch64_dll.bat拷贝到APP安装文件下的Win64文件夹名称内

8、进到安装文件下的win64 文件夹名称寻找mgls.dll mgls64.dll2个文档,鼠标右键点一下特性,除掉写保护特性。

9、运作patch_dll.bat转化成license文档后会自行用文本编辑器开启license.txt.转化成的license.txt,储存在安装文件中

10、鼠标右键点一下我的电脑,点一下特性>高級系统配置>高級>系统变量>新创建,新创建客户系统变量【MGLS_LICENSE_FILE】,变量值为license置放的文件目录,比如:【C:\modeltech64_10.5\win64\LICENSE.TXT】,点一下确认就可以破译取得成功